前言

这门课就是通俗意义上的数电实验,是EE专业基础实验课之一,应该是绝大多数电子信息类专业的必修课。为什么是绝大多数呢,因为呢喃的通信工程专业居然是选修数电及数电实验。一开始我还没有意识到这样的培养方案能带来多抽象的结果,直到在电子学基础II实验课上通信专业的组员问我与运算是什么意思,我愕然。由此可见这个培养方案……

我前段时间想要写这个帖子的时候碰巧知乎刷到了对这门课的评价:“除了zj老师班其他班的要求普遍低于同等院校”。本来还想喷这门实验课的,后来想来也是这样。这门课自从改革成虚拟实验之后已经不需要使用面包板搭建实际电路了,完全基于FPGA进行,在电路排错上节约了大量的时间,事实上这门课的大纲要求和传统实验没有任何区别。

计算机学院也在这个学期开设了数电实验,相比之下,计算机学院的数电实验主要任务是写verilog代码,更注重算法实现。而电子学院的这门课更注重对模块器件的理解和使用,VHDL代码仅仅是作为连接硬件与设计的一环。

那话说回来,我最想说的一点其实是这门课程的资料设置不合理。所有的资料都放在一张table里面,大概是五十多个链接,包含安装文件,安装教程,课程PPT,课程视频讲解(基本就是念PPT),课程文档等等。这些资料之间逻辑关系极差,对于实验的要求甚至可以分开出现在PPT和文档中,对于一些细节或者是注意事项的说明也分散在各个链接当中,甚至非常关键的信息隐藏在文档的注释部分。另外文档是基本不提供实验思路和芯片手册的,只会做最基本的说明,还需要额外花大精力去查找资料。课上的时间基本完全交给你,老师只做验收工作,答疑在课程群进行,并且zj会出现经常不在的情况。尤其是今年我们换了安路的国产开发板,出现了各种zj自己都不知道的问题需要我们来排查,整体而言花费了很多不必要的精力。

这门课数字化实验的尝试是很好的,如果这门课好好改那确实有潜力成为示范性的实验课。可惜目前课堂教学和资料完全无法与之匹配,所有能不选还是别选吧。

另外这门课在最后一节课会进行随堂考试,形式类似于前三节课的黑盒实验,内容也比较接近,评分完全在table中提交进行。注意这次考试在最终成绩当中的占比比较大,平时实验内容做不出来反倒没那么大关系。

这门课作业的答案我完整上传了github,但是我觉得参考这篇文章其实已经可以比较顺利地完成实验了,因此在此就不附上答案链接了,有需要可以自行去github搜索。

实验逻辑

在Multisim中创建PLD子电路,在子电路中绘制原理图,可以导出为VHDL代码,交由通用编程器编译下载到FPGA板子上,运行测试。仿真测试在Multisim的PLD子电路外部或者内部进行。

硬件外设说明

说明基于新换的一批安路EG4S20BG256定制开发板。

由于课程资料不提供开发板原理图,这里附上相近型号开发板的原理图和说明。

1.拨码开关

向上输入高电平,向下输入低电平。从左向右依次是SW7-SW0。

2.LED

高电平有效。如果不做配置引脚处于悬空状态会发出微亮的光。拨码开关上方的LED序号与拨码开关一一对应,从左到右依次是LED7-LED0,键盘矩阵上方从左向右依次是LED11-LED14。

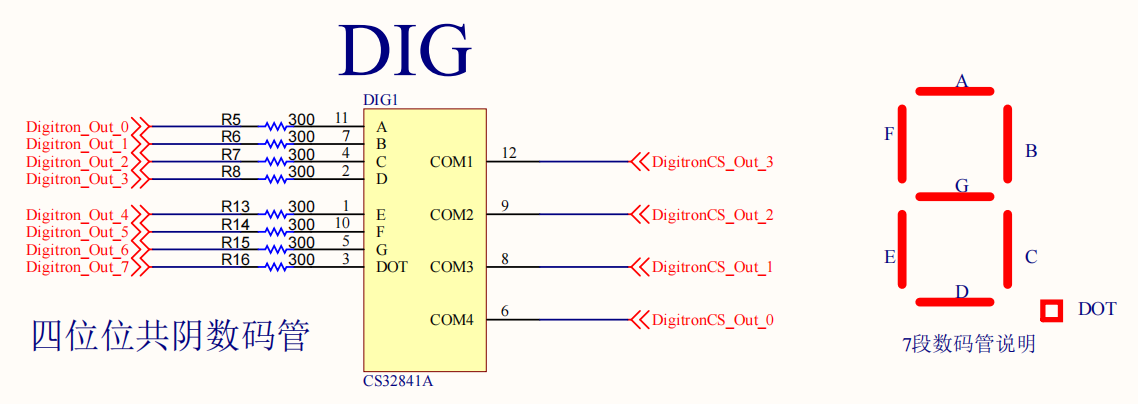

3.数码管

数码管是共阴数码管,高电平有效,从左到右依次编号3-0。注意,为了节约硬件资源,四个数码管共用一套(七个)灯管控制信号,也就是说,这七个灯管控制信号同时连接了四个数码管的同一个位置。因此,如果需要分开控制这四个数码管,需要配合选通信号进行动态刷新。四个数码管各有一个选通信号,低电平有效。在每一个时刻可以选择只让一个选通信号有效,在同一时刻输入这一位的灯管控制信号,随后在下一个时刻让下一个数码管的选通信号有效,输入这一位的灯管控制信号,循环往复。

在用户数据库中提供了MD3048系列模块实现这一功能,但是后续实验中会要求设计这一模块。注意低电平有效和数码管译码模块要使用74MP79共阴模块即可。

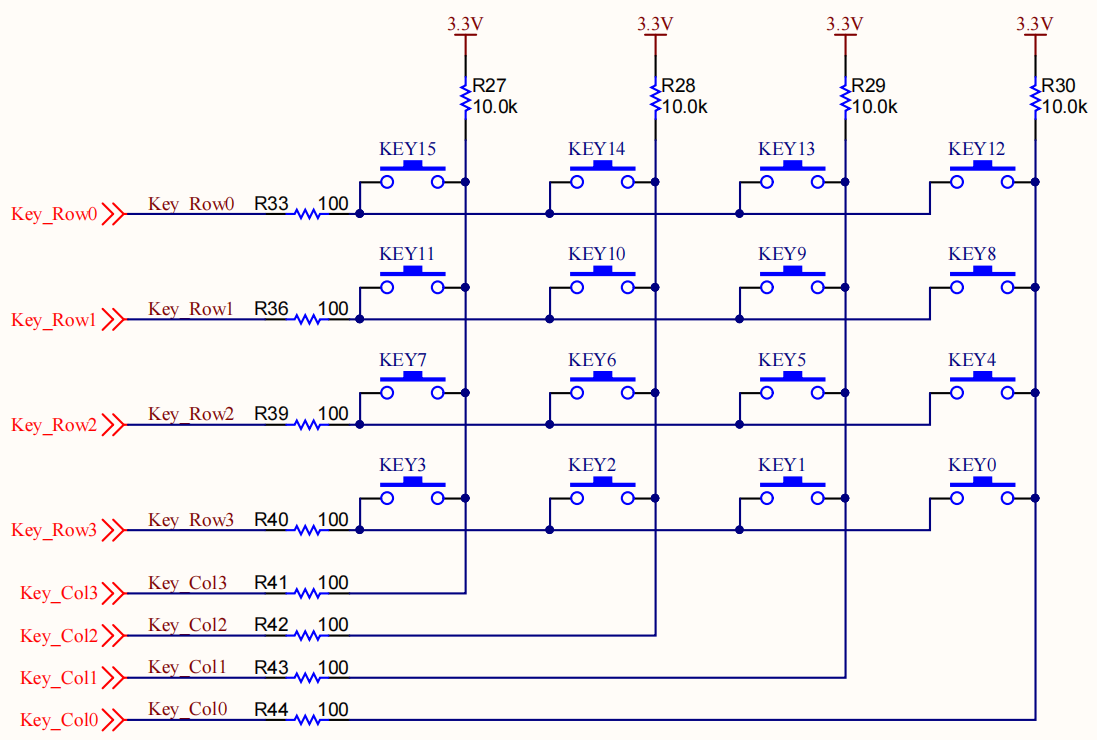

4.键盘矩阵

键盘为行和列扫描,必须使用列作为输入,同时也必须行作为输出,原因是我们需要将行信号接入低电平,这样在这一行中间的一个按键被按下后,相应的电平才会被拉低。因此按键的有效信号是低电平。根据原理图,由于对于需要使用的行我们都需要将行信号接低电平,因此在同一列上的任何按键被按下时,列信号都会得到低电平。也就是说,我们没有办法分辨一列上的哪个按键被按下。因此如果需要让十六个按键都有效,我们需要使用和动态刷新类似的动态扫描方案。这里不多赘述了。行号和列号分别从上到下从左到右为3-0。

附上原理图一张,便于理解。

软件配置说明

由于课程资源已经给出了详细的安装教程,这里只对部分内容进行说明。

Multisim软件版本

请务必安装Multisim14.2或者更新版本。电子学基础I实验安装的14.0版本不能正常使用PLD功能。直接使用安装包升级即可,无需卸载重装。

特别特别注意,安装时如有要求填写用户名,务必填写英文,否则将导致生成的VHDL代码中author项为中文,后续不能编译。

如果你不幸使用了中文用户名(简单判别方法就是在软件的启动界面右下角会显示注册的用户名),那么请使用注册表编辑器修改“计算机\HKEY_LOCAL_MACHINE\SOFTWARE\WOW6432Node\National Instruments\Circuit Design Suite\14.3\Common”路径(将其中的14.3替换为你使用的Multisim版本)下的RegisteredOwner注册表项为英文。

打开软件提示找不到主数据库(以及其他两个数据库)

Windows背锅。一开始在2025年8月win11 24H2某个累积更新之后出现,卸载能解决。后发现未安装该更新的电脑也出现了相关问题,安装后卸载该更新的电脑也不能解决。因此具体原因不得而知。根本原因应该还是windows加强了对于三方软件访问权限的管理,但是没有明确的解决方案我们也无从求证。最简单粗暴的办法:关掉之后重开若干次Multisim。能彻底解决的办法:使用Windows10系统(或者虚拟机)。这个视频评论区中给出了各种解决方案,有兴趣的可以试试。

用户数据库中没有器件

两种情况,第一种是上述找不到数据库的情况,参照上面的方法解决。第二种情况是没有创建PLD子电路,由于用户数据库中全部都是PLD器件,因此只有在PLD子电路中才能正常显示。

初次使用通用编程器报错

检查安装路径中是否包含中文和特殊字符,尽量控制路径下各个文件夹名称不超过八个字符。

模块说明

由于用户模块为zj亲自编写,没有全部经过验证,因此存在不少未被发现的bug。对于用户模块的使用,不管出现什么问题,都记得先查数据手册。推荐半导小芯软件。对于用户模块的芯片,将其中的MP替换为LS即为常用型号,可以直接在半导小芯搜索数据手册。数据手册主要关注模块时序图,真值表,输入输出端的高低电平有效,同步还是异步触发。

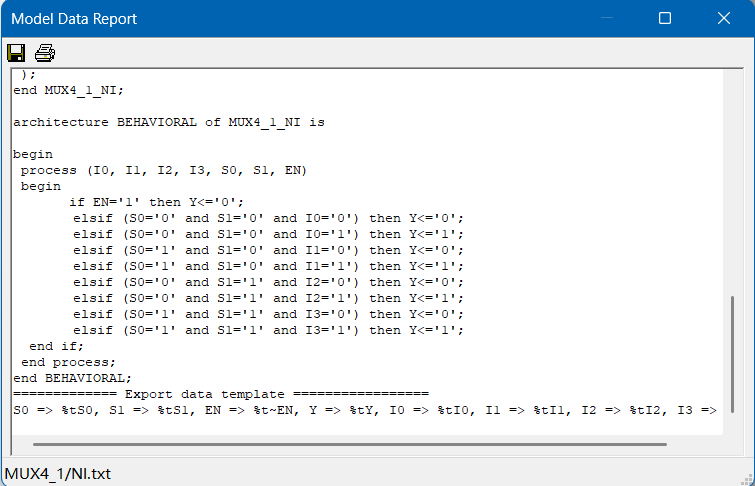

针对没有记载、不可理喻的bug,可以采用以下方法交给ai判断模块是否有问题:右击该模块,properties,view model,将其中的代码复制交给ai解读。

4to1多路选择器

主数据库中的这个模块代码就是有问题的,由于VHDL写成了真值表的形式,因此在编译之后出现了对时钟边沿信号不敏感的情况。表现为可以编译但是没有输出。另外由于用户数据库中的74MP153照抄了这段代码,因此也不能正常使用。

解决方式:使用8to1mux替代,或者自行手搓。

74MP160

用户数据库中该模块的RCO进位信号是同步输出,也就是在计数达到9之后会等待下一个时钟信号上升沿之后才会产生进位信号,与正常的74LS160不同。因此使用该模块时判断进位请使用QA&QD。

74MP164和74MP165

用户数据库中这两个模块均不能正常使用。请分别使用主数据库中的SR_8S_P和SR_8P_S替代。

74MP73

这个下降沿触发的JK触发器不可用,编译失败。请使用上升沿触发的JK触发器,将时钟信号取反替代。

综合实验思路梳理

秒表电路设计

整体框架部分不做赘述,跟着文档连线就完了。

时钟分频器

十分频部分使用五进制计数器结合T触发器翻转电平即可得到。

五分频部分由于不强调占空比(因为所有器件都是基于上升沿触发),因此仍可以使用五进制计数器,使用逻辑门对2和4分别进行检测,通过或门后接入T触发器翻转电平得到,如果需要得到占空比50%的五分频,可以参考这个帖子的思路。大致就是基于上升沿和下降沿分别产生40%占空比的五分频数字信号,让后做或运算即可。这里帖主使用了下降沿触发的D触发器,但是数据库中没有提供,因此我本来想用下降沿触发的JK触发器改,奈何出现了编译失败。经舍友提醒直接将输入时钟信号取反使用原电路就行。

计数电路

思路可以照抄文档给的10000计数电路,将第三位的进位改成5判断就行。另外注意74MP160模块的异步进位信号问题,请手动使用9判断作为进位信号。

按键状态机

按照理论课上讲的,其实就是一个Mealy型的时序逻辑电路。但是由于有四个输入,我觉得工作量有一点点大,因此采用计数器实现状态机。将按键的输入作为时钟信号(不用担心抖动,因为逻辑门的时延已经帮我们做过去抖了),将非顺序转换的状态使用置数和清零功能进行跳转,顺序转换的状态使用正向计数功能。由于置数和清零都需要异步,我只找到了一个符合条件的计数器74MP193。注意该模块反向计数功能不使用时反向计数时钟信号需要输入高电平。

动态刷新数码管

思路是产生四位计数序列,四个状态分别控制一个数码管的选通,同时控制四个多路选择器输出对应数码管需要显示的数字的四位BCD码,然后交给74MP49进行译码输出到数码管。

两个注意点。其一是使用计数器进行计数时会产生奇妙的时延bug,参考学长的方案使用CNTR_4BIN_AS产生计数序列可以解决。其二是74MP49的BI输入高电平才能正常工作,原因是BI是低电平有效的禁止位,相当于高电平有效的使能位。

锁相环测试

验证性实验,如果原理看不懂请参见另一位学长的博客,其他就提两点。

1、基本锁相测试的时候记得把3,4,脚之间连起来形成反馈回路。

2、倍频电路中同步的范围需要包含倍频后的信号频率而不是倍频之前的。

占空比测量仪

计数器

使用74MP160级联即可。注意不要复用分频用的计数器,会有莫名其妙的错误。计数结束不用清零,否则异步的清零会导致在脉冲信号下先被清零后被送数,让其循环计数即可,或者使用同步置数置零也可。

寄存器

建议使用两个D触发器级联。第一路使用待测量信号下降沿产生一个脉冲来触发,第二路采用1Hz时钟触发,减少数码管抖动。

脉冲产生

D触发器输入与反相输出做与运算即可。

100分频

随你怎么做,老师也给了参考电路,注意进位信号问题。

串行数据传输电路

不是很想多说。因为如果八周结课的话来不及做这个,做了的话测试也不好测试,能做出来的也不多。文档叽里咕噜,该给的其实都给了。

控制生成模块不要听他的,实现功能很简单,判断报头来了之后产生一个送数脉冲,送数脉冲之后延迟一个时钟周期产生清零脉冲即可。传入的时钟信号加一个反相器做半个周期的延迟,防止出现时钟信号超前于数据信号导致的传输错位。

将代码烧录到两块板子的方法:期中一块板子同时插上USART和JTAG,然后拔下JTAG,这时USART为其供电,此时再将线插上另一块板子即可。